DS90UB914A-Q1

SNLS499B - APRIL 2016-REVISED OCTOBER 2016

# DS90UB914A-Q1 25-MHz to 100-MHz 10/12-Bit FPD-Link III Deserializer

### 1 Features

- Qualified for Automotive Applications AEC-Q100

- Device Temperature Grade 2: –40°C to +105°C

Ambient Operating Temperature Range

- Device HBM ESD Classification Level ±8kV

- Device CDM ESD Classification Level C6

- 25-MHz to 100-MHz Input Pixel Clock Support

- Programmable Data Payload:

- 10-bit Payload up to 100 MHz

- 12-bit Payload up to 75 MHz

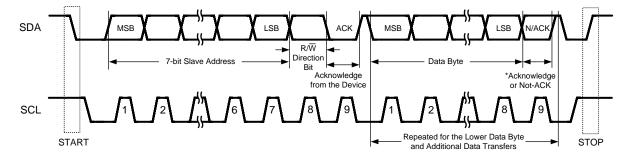

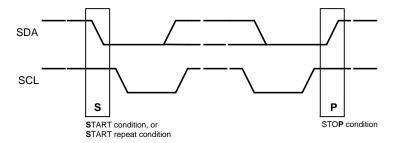

- Continuous Low Latency Bidirectional Control Interface Channel with I2C Support at 400 kHz

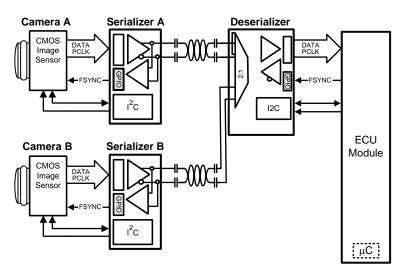

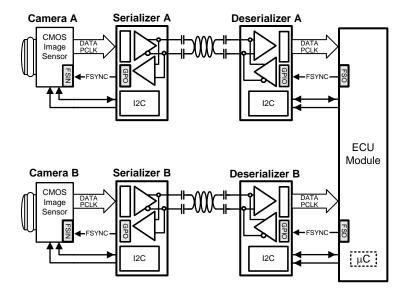

- 2:1 Multiplexer to choose between two input images

- Capable of Receiving over 15m Coaxial or 20m Shielded Twisted-pair Cables

- Robust Power-Over-Coaxial (PoC) Operation

- Receive Equalizer Automatically Adapts for Changes in Cable Loss

- LOCK Output Reporting Pin and @SPEED BIST Diagnosis Feature to Validate Link Integrity

- Single Power Supply at 1.8 V

- ISO 10605 and IEC 61000-4-2 ESD Compliant

- EMI/EMC Mitigation with Programmable Spread Spectrum (SSCG) and Receiver Staggered Outputs

### 2 Applications

- Automotive

- Surround View Systems (SVS)

- Rear and Front View Cameras

- Driver Monitor Cameras (DMS)

- Remote Satellite RADAR Sensors

- Security and Surveillance

- Industrial Machine Vision

### 3 Description

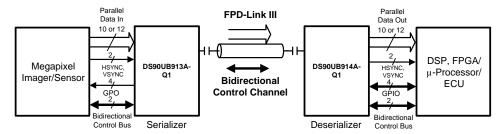

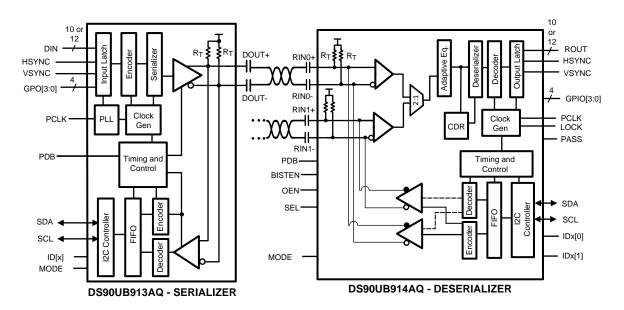

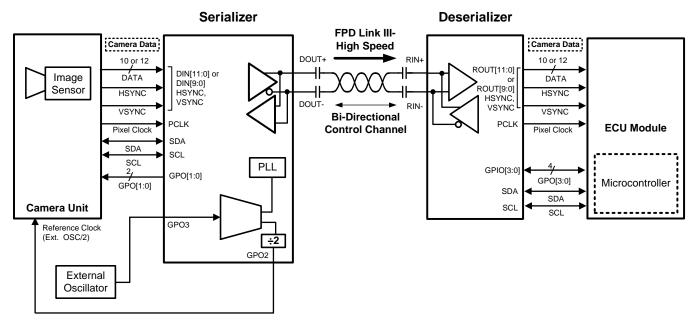

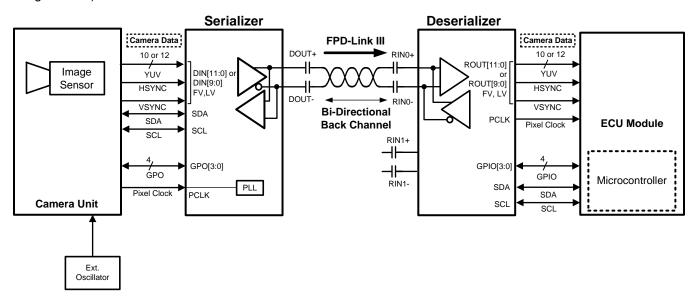

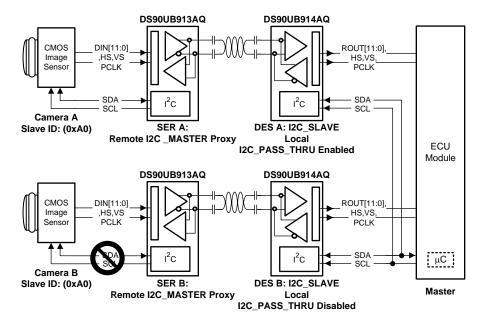

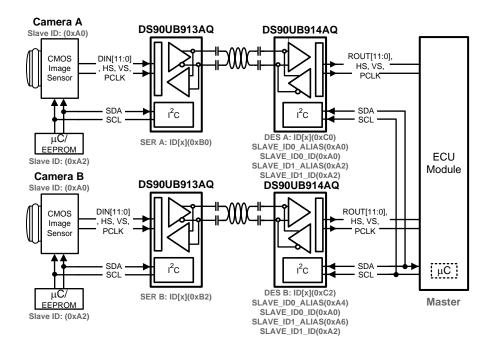

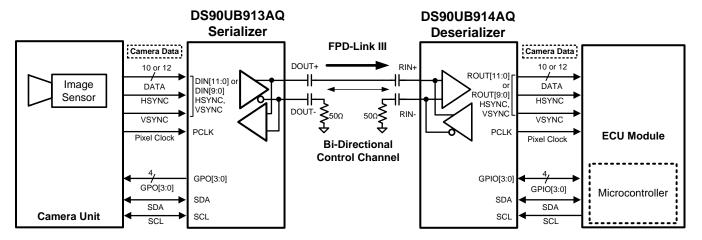

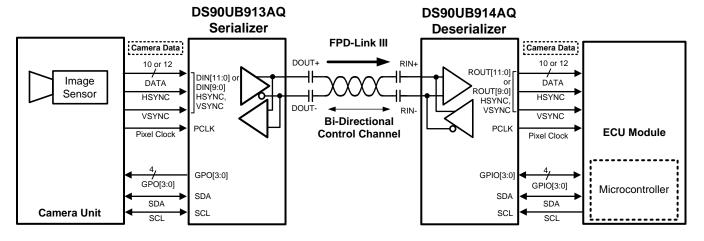

The DS90UB914A-Q1 device offers an FPD-Link III interface with a high-speed forward channel and a bidirectional control channel for data transmission over a single coaxial cable or differential pair. The DS90UB914A-Q1 device incorporates differential signaling on both the high-speed forward channel and bidirectional control channel data paths. The deserializer is targeted for connections between imagers and video processors in an ECU (Electronic Control Unit). This device is ideally suited for driving video data requiring up to 12-bit pixel depth plus two synchronization signals along with bidirectional control channel bus.

The deserializer features a multiplexer to allow selection between two input imagers, one active at a time. The primary video transport converts 10-bit or 12-bit data to a single high-speed serial stream, along with a separate low latency bidirectional control channel transport that accepts control information from an I2C port and is independent of video blanking period.

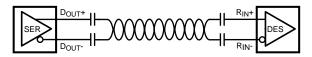

Using TI's embedded clock technology allows transparent full-duplex communication over a single differential pair, carrying asymmetrical-bidirectional control channel information. This single serial stream simplifies transferring a wide data bus over PCB traces and cable by eliminating the skew problems between parallel data and clock paths. This significantly saves system cost by narrowing data paths that in turn reduce PCB layers, cable width, and connector size and pins. In addition, the Deserializer inputs provide adaptive equalization to compensate for loss from the media over longer distances. Internal DC-balanced encoding/decoding is used to support AC-coupled interconnects.

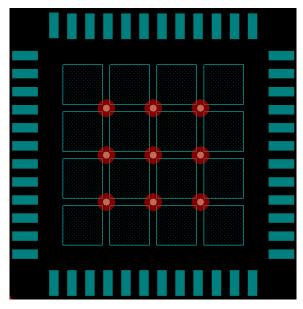

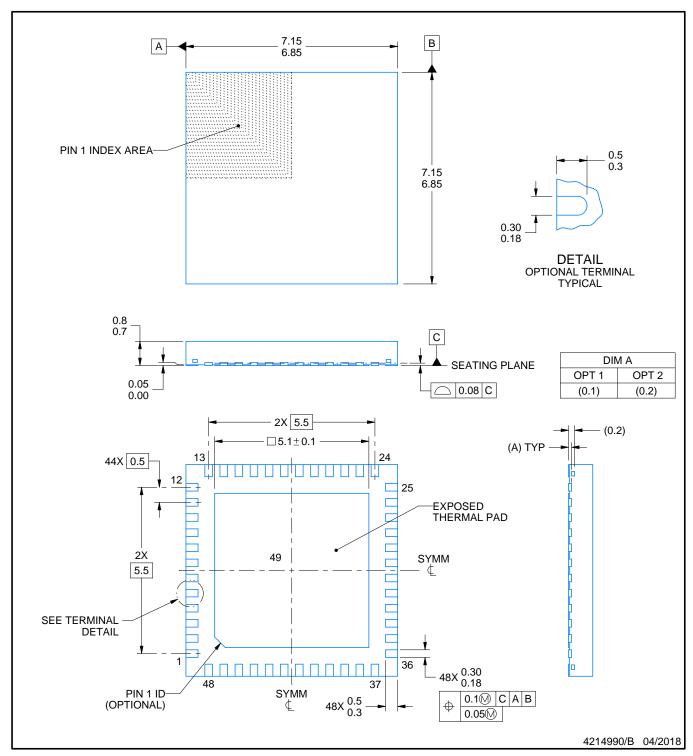

### **Device Information**(1)

| PART NUMBER   | PACKAGE   | BODY SIZE (NOM)   |  |

|---------------|-----------|-------------------|--|

| DS90UB914A-Q1 | WQFN (48) | 7.00 mm x 7.00 mm |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

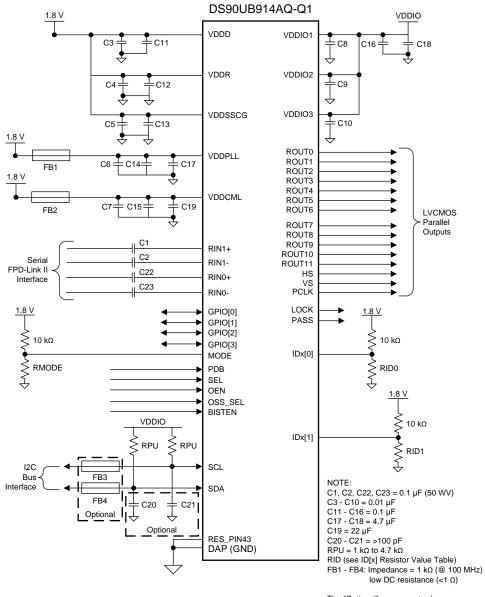

### **Simplified Schematic**

Copyright © 2016, Texas Instruments Incorporated

# **Table of Contents**

| 2 Applications 1 1 8.4 Device Functional Modes 8.5 Programming 8.6 Register Maps 8.6 Register Maps 9 Application and Implementation 9.1 Application Information 9.2 Typical Applications 9.2 Typical Application 9.2 Typical Application 9.2 Typical Application 9.2 Typical Applications 9.2 Typical Applications 9.2 Typical Applications 9.2 Typical Application 9.2 T | 19               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 3 Description 1 1 8.5 Programming 8.6 Register Maps 9 Application and Implementation 9.1 Application and Implementation 9.1 Application and Implementation 9.1 Application Information 9.2 Typical Applications 7 T.1 Absolute Maximum Ratings 7 T.2 ESD Ratings 7 T.3 Recommended Operating Conditions 7 T.4 Thermal Information 8 T.5 Electrical Characteristics 8 T.6 AC Timing Specifications (SCL, SDA) - I2C-Compatible 12 T.7 Bidirectional Control Bus DC Timing Specifications (SCL, SDA) - I2C-Compatible 13 T.8 Deserializer Switching Characteristics 15 T.9 Typical Characteristics 17 Typical Characteristics 17 Typical Characteristics 17 Typical Characteristics 18 Detailed Description 18 S.5 Programming 8.6 Register Maps 9 Application and Implementation 9.1 Application Information 9.1 Application Information 9.2 Typical Applications 11 Layout 9.1 Applications 9.2 Typical Applications 11.1 Layout Guidelines 11.2 Layout Example 11.2 Documentation Support 12.2 Receiving Notification of Documentation 12.3 Community Resources 12.3 Community Resources 12.4 Trademarks 12.5 Electrostatic Discharge Caution 12.6 Glossary 12. | <u>23</u>        |

| 4 Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |

| 5 Device Comparison Table 4 6 Pin Configuration and Functions 4 7 Specifications 7 7.1 Absolute Maximum Ratings 7 7.2 ESD Ratings 7 7.3 Recommended Operating Conditions 7 7.4 Thermal Information 8 7.5 Electrical Characteristics 8 7.6 AC Timing Specifications (SCL, SDA) - I2C-Compatible 12 7.7 Bidirectional Control Bus DC Timing Specifications (SCL, SDA) - I2C-Compatible 13 7.8 Deserializer Switching Characteristics 15 7.9 Typical Characteristics 17 8 Detailed Description 18 8.1 Overview 18 9 Application and Implementation 9.1 Application and Implementation 9.1 Application Information 9.2 Typical Impormation 19.2 Typical Applications (9.2 Typical Applications 10 9.1 Application Information 9.1 Application Information 9.2 Typical Applications 10 9.2 Typical Application Information 9.2 Typical Applications 11 1 Layout 11.1 Layout Guidelines 11.2 Layout Example 11.2 Layout Exam | 34               |

| 6 Pin Configuration and Functions 4 7 Specifications 7 7.1 Absolute Maximum Ratings 7 7.2 ESD Ratings 7 7.3 Recommended Operating Conditions 7 7.4 Thermal Information 8 7.5 Electrical Characteristics 8 7.6 AC Timing Specifications (SCL, SDA) - I2C- Compatible 12 7.7 Bidirectional Control Bus DC Timing Specifications (SCL, SDA) - I2C-Compatible 13 7.8 Deserializer Switching Characteristics 15 7.9 Typical Characteristics 17 8 Detailed Description 18 8.1 Overview 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45               |

| 7 Specifications. 7 7.1 Absolute Maximum Ratings 7 7.2 ESD Ratings. 7 7.3 Recommended Operating Conditions 7 7.4 Thermal Information 8 7.5 Electrical Characteristics 8 7.6 AC Timing Specifications (SCL, SDA) - I2C- Compatible 12 7.7 Bidirectional Control Bus DC Timing Specifications (SCL, SDA) - I2C- Compatible 13 7.8 Deserializer Switching Characteristics 15 7.9 Typical Characteristics 17 8 Detailed Description 18 8.1 Overview 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45               |

| 7.1 Absolute Maximum Ratings 7 7.2 ESD Ratings 7 7.3 Recommended Operating Conditions 7 7.4 Thermal Information 8 7.5 Electrical Characteristics 8 7.6 AC Timing Specifications (SCL, SDA) - I2C- Compatible 12 7.7 Bidirectional Control Bus DC Timing Specifications (SCL, SDA) - I2C- Compatible 13 7.8 Deserializer Switching Characteristics 15 7.9 Typical Characteristics 17 8 Detailed Description 18 8.1 Overview 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 48               |

| 7.2 ESD Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <mark>52</mark>  |

| 7.2 ESD Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53               |

| 7.4 Thermal Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |

| 7.5 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  |

| 7.6 AC Timing Specifications (SCL, SDA) - I2C- Compatible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |

| Compatible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  |

| 7.7 Bidirectional Control Bus DC Timing Specifications (SCL, SDA) - I2C-Compatible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |

| (SCL, SDA) - I2C-Compatible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •                |

| 7.9 Typical Characteristics 17 12.6 Glossary 12.6 Glossary 18 Detailed Description 18 13 Mechanical, Packaging, and Orderable Information 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |

| 7.9 Typical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <u>5</u> 6       |

| 8 Detailed Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |

| 8.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <mark>5</mark> 6 |

| 8.2 Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |

# 4 Revision History

# Changes from Revision A (June 2016) to Revision B

| Page |

|------|

|------|

| • | Added Back Channel Line Rate specification; also added footnote for clarification between MHz and Mbps distinction | . 9 |

|---|--------------------------------------------------------------------------------------------------------------------|-----|

| • | Revised back channel VOD specification from 175mV to 182 mV.                                                       | . 9 |

| • | Removed 'ns' unit from specifications referencing period in units of T.                                            | 16  |

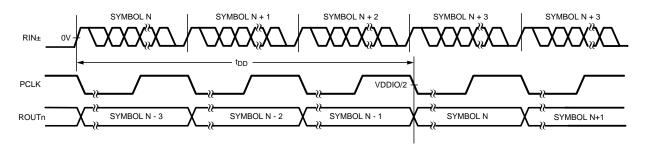

| • | Revise Deserializer Delay specification due to the swapped information.                                            | 16  |

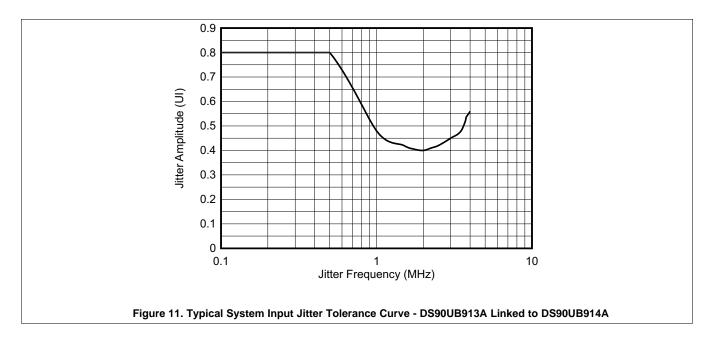

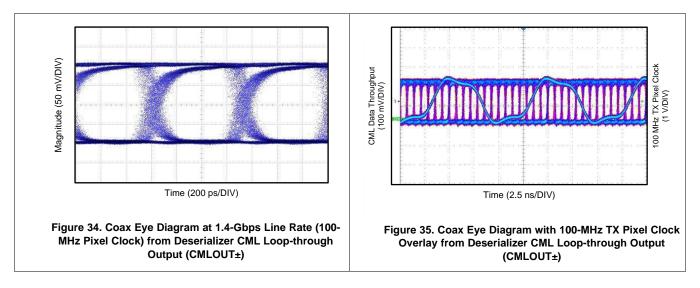

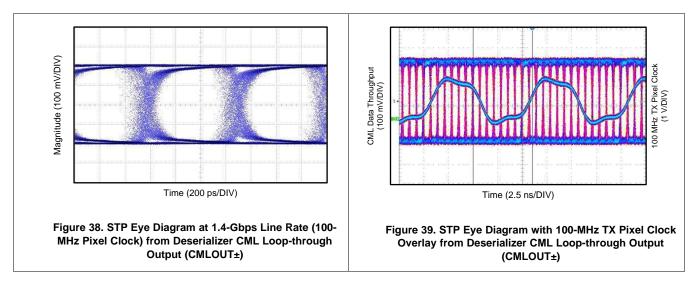

| • | Revised jitter tolerance curve to be for typical system IJT configuration with DS90UB913A linked to DS90UB914A     | 17  |

| • | Added device functional mode table for external oscillator operation with example XCLKIN = 48MHz                   | 23  |

| • | Fixed typo and changed "deserializer" to "serializer"                                                              | 35  |

| • | Added register 0x05 for Forward Channel Low Frequency Gain.                                                        | 35  |

| • | Added registers 0x27, 0x47 for Forward Channel Tuning/Impedance Control.                                           | 43  |

| • | Revised rise time and delay conditions to include 10% to 90% parameters instead of VIH and VIL.                    | 46  |

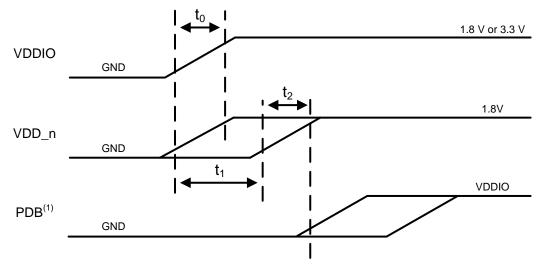

| • | Changed max rise time for $V_{DDIO}$ and $V_{DD_N}$ to be 5ms instead of 1.5ms during power-up.                    | 46  |

| • | Revised power-up timing paragraph for clarity and correctness.                                                     | 46  |

| • | Changed VIL and VIH specs to 10% and 90% respectively for rising/falling edges.                                    | 46  |

# Changes from Original (April 2016) to Revision A

### Page

| • | Split document into two separate documents for parts DS90UB913A-Q1 SNLS443 and DS90UB914A-Q1 SNLS499                                                                                | 1 |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| • | Combined revision history showing changes when this document was part of the DS90UB913A-Q1 SNLS443 datasheet                                                                        | 1 |

| • | Added Automotive Features                                                                                                                                                           | 1 |

| • | Updated pin description for ROUT to include active/inactive outputs corresponding to MODE setting                                                                                   | 4 |

| • | Added pin description to GPIO pins to leave open if unused.                                                                                                                         | 5 |

| • | Updated frequency requirements for 10-bit and 12-bit HF modes. 10-bit mode – 50 MHz to 100 MHz; 12-bit HF mode – 37.5 MHz to 75 MHz; 12-bit LF mode (no change) – 25 MHz to 50 MHz. | 5 |

| • | Added pin description to RIN pins to leave open if unused.                                                                                                                          | 6 |

Submit Documentation Feedback

| • | Changed Air Discharge ESD Rating (IEC61000-4-2: RD = 330 Ω, CS = 150 pF) to minimum ±25000 V                                                                                                                                                                                                                                                 | 7        |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| • | Added additional thermal characteristics                                                                                                                                                                                                                                                                                                     | 8        |

| • | Added GPIO[3:0] typical pin capacitances.                                                                                                                                                                                                                                                                                                    | 8        |

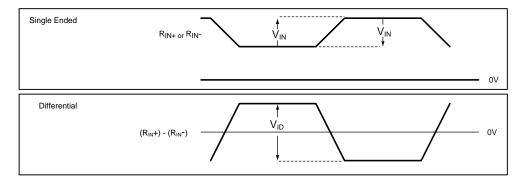

| • | Changed Differential Input Voltage minimum specification.                                                                                                                                                                                                                                                                                    | 9        |

| • | Changed Single-Ended Input Voltage minimum specification                                                                                                                                                                                                                                                                                     | 9        |

| • | Added Back Channel Differential Output Voltage minimum specification.                                                                                                                                                                                                                                                                        | 9        |

| • | Added Back Channel Single-Ended Output Voltage minimum specification                                                                                                                                                                                                                                                                         | 9        |

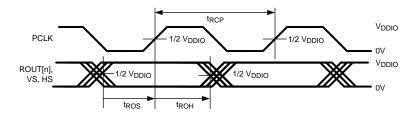

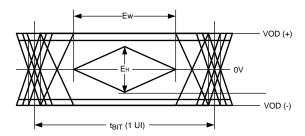

| • | Added footnote that states the following: "UI – Unit Interval is equivalent to one serialized data bit width. The UI scales with PCLK frequency." Also added below calculations to footnote. 12-bit LF mode 1 UI = 1 / ( PCLK_Freq. x 28 ) 12-bit HF mode 1 UI = 1 / ( PCLK_Freq. x 2/3 x 28 ) 10-bit mode 1 UI = 1 / ( PCLK_Freq. /2 x 28 ) | <u>ç</u> |

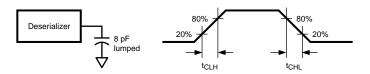

| • | Updated I <sub>DDIOR</sub> for V <sub>DDIO</sub> =1.89V, C <sub>L</sub> =8pF, Worst-Case Pattern with f=50 MHz, 12-bit low freq mode to typical value of 16 mA; value is currently 21 mA.                                                                                                                                                    | 10       |

| • | Updated I <sub>DDIOR</sub> for V <sub>DDIO</sub> =1.89V, C <sub>L</sub> =8pF, Random Pattern with f=50 MHz, 12-bit low freq mode to typical value of 10 mA; value is currently 14 mA                                                                                                                                                         | 10       |

| • | Updated $I_{DDR}$ for $V_{DD_n}$ =1.89V, $C_L$ =4pF, Random Pattern with f=100 MHz, 10-bit mode to typical value of 69 mA; value is currently 57 mA.                                                                                                                                                                                         | 10       |

| • | Updated I <sub>DDR</sub> for V <sub>DD_n</sub> =1.89V, C <sub>L</sub> =4pF, Random Pattern with f=75 MHz, 12-bit high freq mode to typical value of 71 mA; value is currently 60 mA                                                                                                                                                          | 10       |

| • | Updated $I_{DDR}$ for $V_{DD\_n}$ =1.89V, $C_L$ =4pF, Random Pattern with f=50 MHz, 12-bit low freq mode to typical value of 67 mA; value is currently 56 mA                                                                                                                                                                                 | 10       |

| • | Updated $V_{OL}$ Output Low Level row with revised $I_{OL}$ currents and max $V_{OL}$ voltages, dependent upon $V_{DDIO}$ voltage                                                                                                                                                                                                            | 13       |

| • | Updated Figure 2 title to state "Worst-Case" Test Pattern for Power Consumption'                                                                                                                                                                                                                                                             | 13       |

| • | Updated Figure 3 "Deserializer Vswing Diagram" with correct notation.                                                                                                                                                                                                                                                                        | 13       |

| • | Changed Figure 3 to clarify difference between STP and Coax                                                                                                                                                                                                                                                                                  | 13       |

| • | Updated frequency ranges for MODE settings and also revised with correct maximum clock periods. Added footnote and nominal clock period to be in terms of 'T'                                                                                                                                                                                | 15       |

| • | Changed typo on footnote to reflect 't <sub>DPJ</sub> '.                                                                                                                                                                                                                                                                                     | 16       |

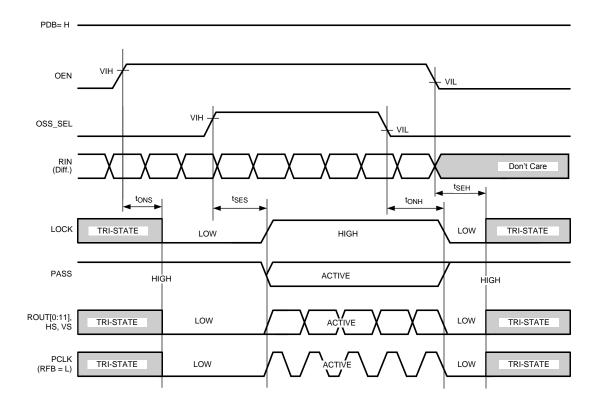

| • | Table 2, row 5 with "static" input LOCK output status changed to "L".                                                                                                                                                                                                                                                                        | 26       |

| • | Table 5 heading updated to state "DS90UB914A-Q1 DESERIALIZER.                                                                                                                                                                                                                                                                                | 32       |

| • | Changed description of deserializer reg 0x00 bit[0]=0 from "set using address coming from CAD" to "set from ID[x]"                                                                                                                                                                                                                           | 34       |

| • | Added row to register 0x01[2] for Back Channel Enable – 0: Disable 1: Enable.                                                                                                                                                                                                                                                                | 34       |

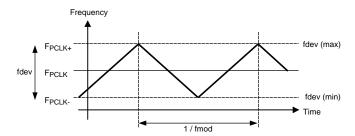

| • | Changed SSCG Units for fmod (register 0x02[3:0]) to Reflect Hz instead of KHz                                                                                                                                                                                                                                                                | 34       |

| • | Changed parity error reset bit to be NOT self-clearing.                                                                                                                                                                                                                                                                                      | 35       |

| • | Changed EQ gain values (dB) @ maximum line rate (1.4Gbps).                                                                                                                                                                                                                                                                                   | 35       |

| • | Changed description of descrializer reg 0x04 to have correct register setting for each equalization gain level                                                                                                                                                                                                                               | 35       |

| • | Added registers 0x26, 0x46 for Bidirectional Control Channel (BCC)Tuning.                                                                                                                                                                                                                                                                    | 43       |

| • | Added deserializer 0x4C SEL register                                                                                                                                                                                                                                                                                                         | 44       |

| • | Updated EQ Register Bits 0x4E[3:0] to be Reserved. Also changed EQ gain values (dB) @ maximum line rate (1.4Gbps)                                                                                                                                                                                                                            | 44       |

| • | Added reference to Power over Coax Application report                                                                                                                                                                                                                                                                                        | 45       |

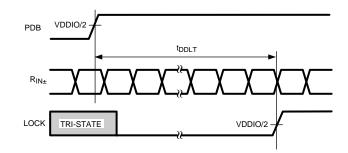

| • | Updated power up sequencing information and timing diagram                                                                                                                                                                                                                                                                                   | 45       |

| • | Added power up sequencing information and timing diagram.                                                                                                                                                                                                                                                                                    | 45       |

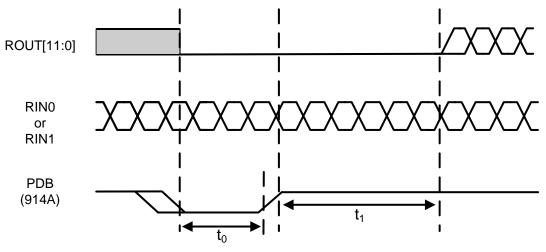

| • | Added 914A PDB Reset timing constraints and diagram.                                                                                                                                                                                                                                                                                         | 46       |

| • | Removed Figure 21 and Figure 43 regarding adaptive equalizer graphs for loss compensation (Coax/STP)                                                                                                                                                                                                                                         | 47       |

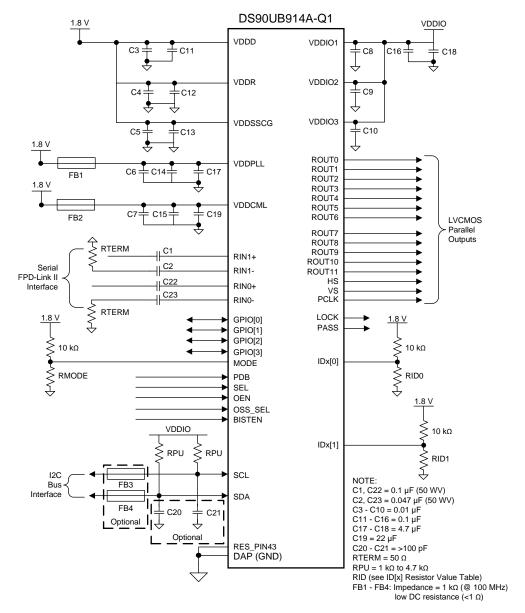

| • | Renamed C1 and C2 to C22 and C23 for RIN0+ and RIN0- respectively on Typical Application Diagrams (Coax & STP).                                                                                                                                                                                                                              | 49       |

| • | Added description specifying that the voltage applied on $V_{DDIO}$ (1.8 V, 3.3 V) or $V_{DD_n}$ (1.8 V) should be at the input pin – any board level DC drop should be compensated.                                                                                                                                                         | 52       |

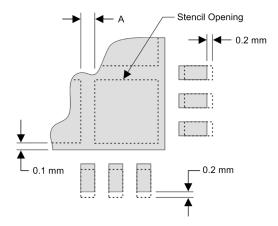

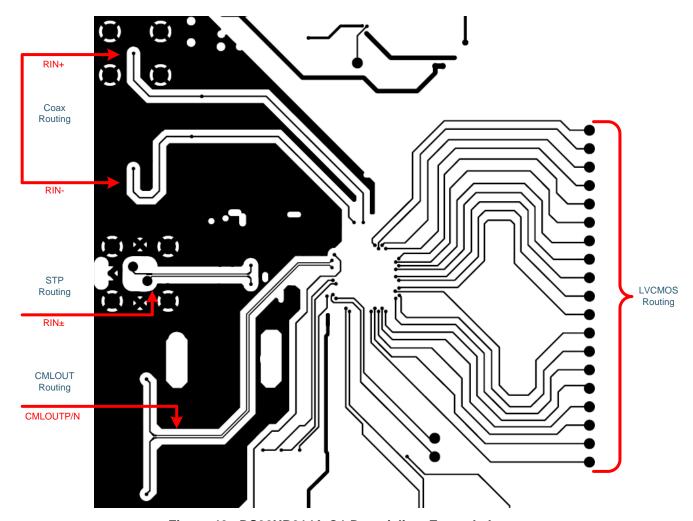

| • | Added 914A EVM layout example image.                                                                                                                                                                                                                                                                                                         | 55       |

### 5 Device Comparison Table

| PART NUMBER FPD-III FUNCTION DS90UB914Q-Q1 Deserializer |  | PACKAGE       | TRANSMISSION MEDIA | PCLK FREQUENCY |  |

|---------------------------------------------------------|--|---------------|--------------------|----------------|--|

|                                                         |  | WQFN RHS (48) | STP                | 10 to 100 MHz  |  |

| DS90UB914A-Q1 Deserializer                              |  | WQFN RHS (48) | Coax or STP        | 25 to 100 MHz  |  |

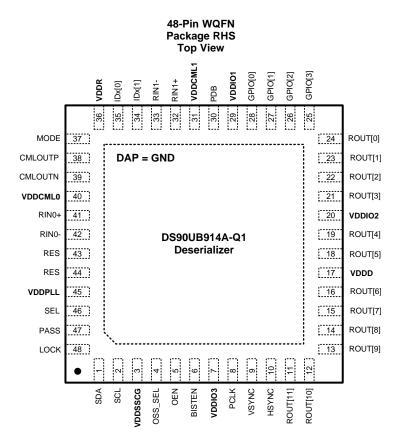

# 6 Pin Configuration and Functions

Pin Functions: DS90UB914A-Q1 Deserializer

| PIN NAME NO.                                     |                           | 1/0                | DECODIDATION                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|--------------------------------------------------|---------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                  |                           | I/O                | DESCRIPTION                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| LVCMOS PAR                                       | LVCMOS PARALLEL INTERFACE |                    |                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| ROUT[11:0] 11,12,13,14, 15,16,18,19, 21,22,23,24 |                           | Outputs,<br>LVCMOS | Parallel Data Outputs For 10-bit MODE, parallel outputs ROUT[9:0] are active. ROUT[11:10] are inactive and should not be used. Any unused outputs (including ROUT[11:10]) should be No Connect. For 12-bit MODE (HF or LF), parallel outputs ROUT[11:0] are active. Any unused outputs should be No Connect. |  |  |  |  |

| HSYNC 10                                         |                           | Output,<br>LVCMOS  | Horizontal SYNC Output. Note: HS transition restrictions: 1. 12-bit Low-Frequency mode: No HS restrictions (raw) 2. 12-bit High-Frequency mode: No HS restrictions (raw) 3. 10-bit mode: HS restricted to no more than one transition per 10 PCLK cycles. Leave open if unused.                              |  |  |  |  |

| VSYNC                                            | 9                         | Output,<br>LVCMOS  | Vertical SYNC Output. Note: VS transition restrictions: 1. 12-bit Low-Frequency mode: No VS restrictions (raw) 2. 12-bit High-Frequency mode: No VS restrictions (raw) 3. 10-bit mode: VS restricted to no more than one transition per 10 PCLK cycles. Leave open if unused.                                |  |  |  |  |

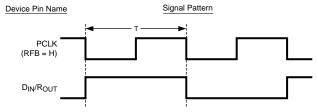

| PCLK                                             | 8                         | Output,<br>LVCMOS  |                                                                                                                                                                                                                                                                                                              |  |  |  |  |

# Pin Functions: DS90UB914A-Q1 Deserializer (continued)

| PIN         |                                                                                                                                                                                         | NO DESCRIPTION                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NAME NO.    |                                                                                                                                                                                         | I/O                                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| GENERAL PU  | GENERAL PURPOSE INPUT/OUTPUT (GPIO)                                                                                                                                                     |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

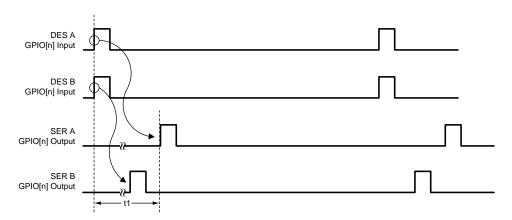

| GPI0[1:0]   | 27,28                                                                                                                                                                                   | Digital<br>Input/Output,<br>LVCMOS | General-purpose input/output pins can be used to control and respond to various commands. They may be configured to be the input signals for the corresponding GPOs on the serializer or they may be configured to be outputs to follow local register settings. Leave open if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| GPIO[3:2]   | 25,26                                                                                                                                                                                   | Digital<br>Input/Output<br>LVCMOS  | General purpose input/output pins GPO[3:2] can be configured to be input signals for GPO on the Serializer. In addition they can also be configured to be outputs to follow the local register settings. When the SerDes chipsets are working with an external oscillator, these pins can be configured only to be outputs to follow the local register settings. Leave open it unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| BIDIRECTION | AL CONTROL                                                                                                                                                                              | BUS - I2C COM                      | MPATIBLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

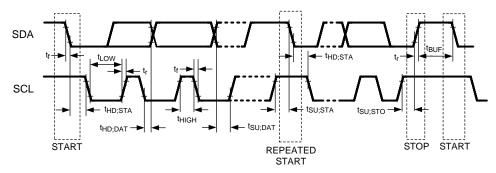

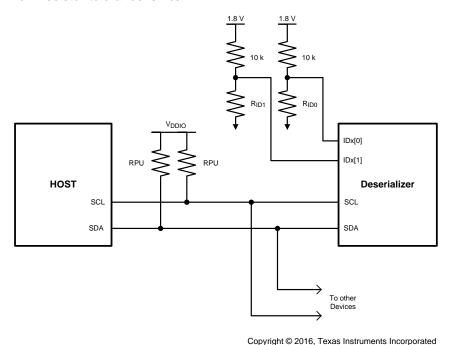

| SCL         | 2                                                                                                                                                                                       | Input/Output,<br>Open Drain        | Clock line for the bidirectional control bus communication SCL requires an external pullup resistor to V <sub>DDIO</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| SDA         | 1                                                                                                                                                                                       | Input/Output,<br>Open Drain        | Data line for bidirectional control bus communication SDA requires an external pullup resistor to V <sub>DDIO</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

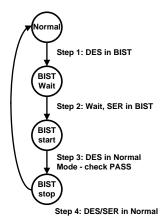

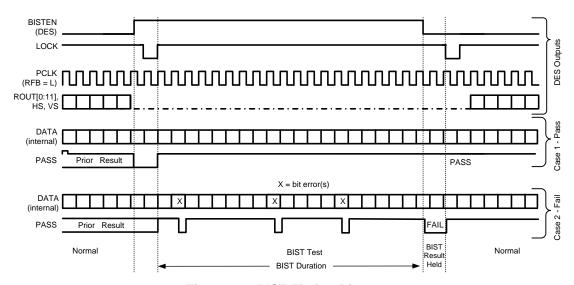

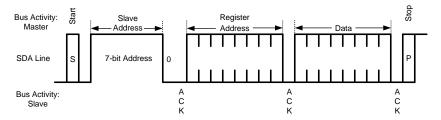

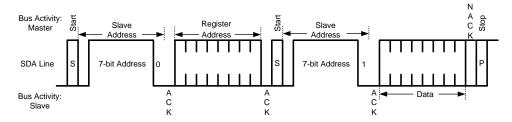

| MODE        | 37                                                                                                                                                                                      | Input, analog                      | Device Mode Select Resistor to Ground and 10-k $\Omega$ pullup to 1.8 V rail. The MODE pin on the Deserializer can be used to configure the Serializer and Deserializer to work in different input PCLK range. See details in Table 2.   12– bit low frequency mode – (25 – 50 MHz operation):   In this mode, the Serializer and Deserializer can accept up to 12-bits DATA+2 SYNC. Input PCLK range is from 25 MHz to 50 MHz. Note: No HS/VS restrictions.   12– bit high frequency mode – (37.5 – 75 MHz operation):   In this mode, the Serializer and Deserializer can accept up to 12-bits DATA + 2 SYNC. Input PCLK range is from 37.5 MHz to 75 MHz. Note: No HS/VS restrictions.   10–bit mode– (50 – 100 MHz operation):   In this mode, the Serializer and Deserializer can accept up to 10-bits DATA + 2 SYNC. Input PCLK frequency can range from 50 MHz to 100 MHz. Note: HS/VS restricted to no more than one transition per 10 PCLK cycles.   Please refer to Table 2 on how to configure the MODE pin on the Deserializer. |  |  |  |  |  |  |